LCMXO1200C-3TN144I FPGA – Feltprogrammerbar gate-array 1200 LUT-er 113 IO 1,8 /2,5/3,3V -3 hastigheter I

♠ Produktbeskrivelse

| Produktattributt | Attributtverdi |

| Produsent: | Gitter |

| Produktkategori: | FPGA - Feltprogrammerbar gate-array |

| RoHS-kode: | Detaljer |

| Serie: | LCMXO1200C |

| Antall logiske elementer: | 1200 LE |

| Antall I/O-er: | 113 I/O |

| Forsyningsspenning - Min: | 1,71 V |

| Forsyningsspenning - Maks: | 3,465 V |

| Minimum driftstemperatur: | - 40 grader Celsius |

| Maksimal driftstemperatur: | + 100 °C |

| Datahastighet: | - |

| Antall sendere/mottakere: | - |

| Monteringsstil: | SMD/SMT |

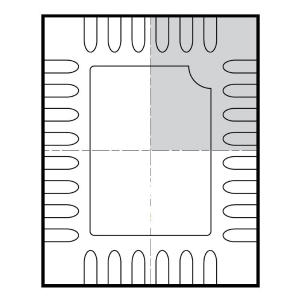

| Pakke/eske: | TQFP-144 |

| Emballasje: | Brett |

| Merke: | Gitter |

| Distribuert RAM: | 6,4 kbit |

| Innebygd blokk-RAM - EBR: | 9,2 kbit |

| Høyde: | 1,4 mm |

| Lengde: | 20 mm |

| Maksimal driftsfrekvens: | 500 MHz |

| Fuktighetsfølsom: | Ja |

| Antall logiske arrayblokker – LAB-er: | 150 LAB |

| Driftsstrøm: | 21 mA |

| Driftsspenning: | 1,8 V/2,5 V/3,3 V |

| Produkttype: | FPGA - Feltprogrammerbar gate-array |

| Fabrikkpakkemengde: | 60 |

| Underkategori: | Programmerbare logiske IC-er |

| Totalt minne: | 15,6 kbit |

| Bredde: | 20 mm |

| Enhetsvekt: | 1,319 g |

Ikke-flyktig, uendelig omkonfigurerbar

• Øyeblikkelig påslag – slås på i løpet av mikrosekunder

• Enkel brikke, ikke nødvendig med eksternt konfigurasjonsminne

• Utmerket designsikkerhet, ingen bitstrøm å avlytte

• Konfigurer SRAM-basert logikk på nytt på millisekunder

• SRAM og ikke-flyktig minne programmerbart via JTAG-port

• Støtter bakgrunnsprogrammering av ikke-flyktig minne

Hvilemodus

• Tillater opptil 100x reduksjon av statisk strøm

TransFR™-rekonfigurasjon (TFR)

• Oppdatering av logikk i felten mens systemet er i drift

Høy I/O til logikktetthet

• 256 til 2280 LUT4-er

• 73 til 271 I/O-er med omfattende pakkealternativer

• Støttet for tetthetsmigrasjon

• Blyfri/RoHS-kompatibel emballasje

Innebygd og distribuert minne

• Opptil 27,6 kbit sysMEM™ innebygd blokk-RAM

• Opptil 7,7 kbit distribuert RAM

• Dedikert FIFO-kontrolllogikk

Fleksibel I/O-buffer

• Programmerbar sysIO™-buffer støtter et bredt spekter av grensesnitt:

– LVCMOS 3.3/2.5/1.8/1.5/1.2

– LVTTL

– PCI

– LVDS, Bus-LVDS, LVPECL, RSDS

sysCLOCK™ PLL-er

• Opptil to analoge PLL-er per enhet

• Klokkemultiplikasjon, divisjon og faseforskyvning

Støtte på systemnivå

• IEEE-standard 1149.1 grenseskanning

• Innebygd oscillator

• Enheter fungerer med strømforsyning på 3,3 V, 2,5 V, 1,8 V eller 1,2 V

• IEEE 1532-kompatibel programmering i systemet